產品簡介

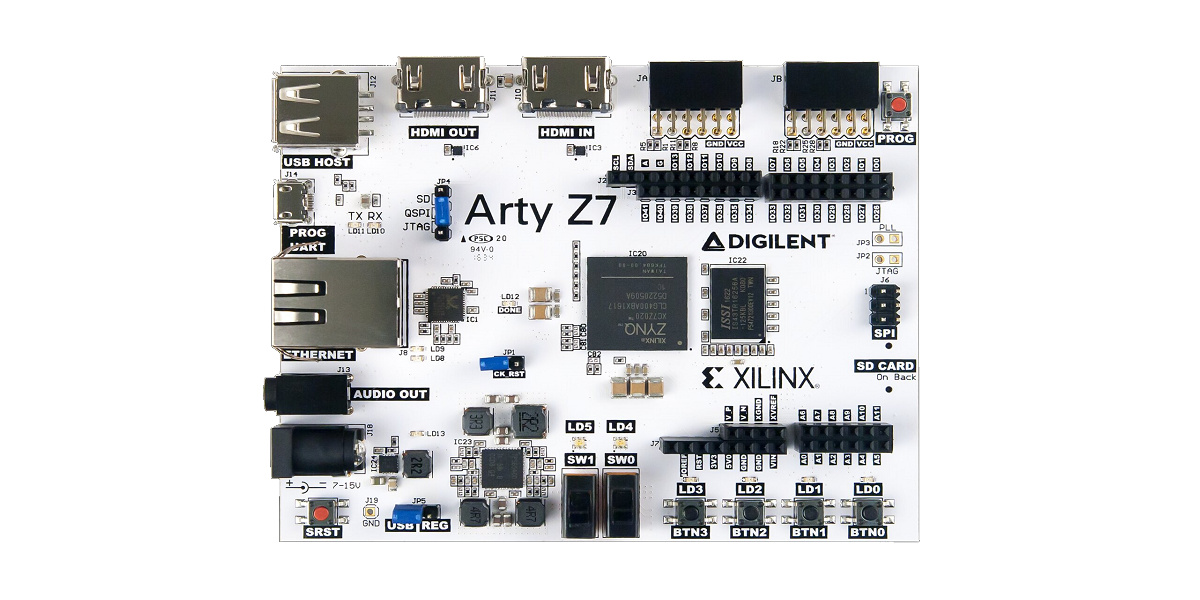

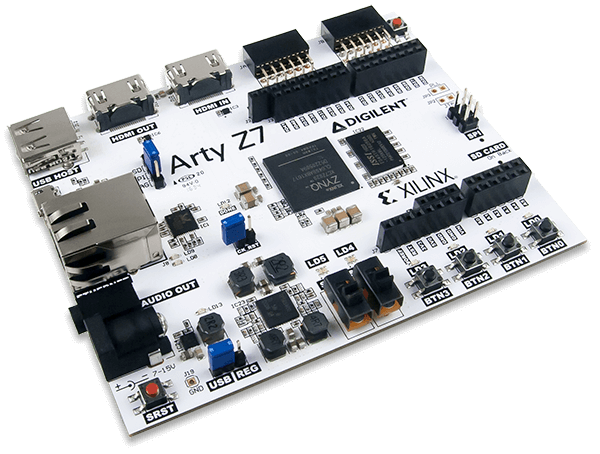

DIGILENT Arty Z7 為即用型開發平台,圍繞 Xilinx Zynq-7000 AP SoC (All Programmable SoC) 所設計。Arty Z7 所使用的 Zynq-7000 架構緊密結合了1個雙核心 650MHz ARM Cortex-A9 處理器及 Xilinx 7系列 FPGA 。此一架構使開發者可根據自身需求,在強大的處理器周圍自訂一套由軟體定義的獨特週邊和控制器,以應對各種不同的應用挑戰。

Arty Z7 為開發者提供了一條系統開發路徑解決方案,使開發者能夠自訂各種不同週邊,並將其功能在 ARM 處理器上實現。 除了內建的2個Pmod介面之外,Arty Z7 並提供 Arduino 介面,使用者可自由地連接各種 Arduino 擴充設備,包括感測器、藍牙、WiFi等周邊的功能。

Arty Z7因其輕便小巧的特色而帶來更為廣泛的可應用性,高畫面播放速率之下進行視訊處理、硬體加速、即時訊號處理、高頻寬、低延遲等處理,可應用於電腦視覺、工業控制、飛行器、嵌入式硬體加速、即時控制等相關領域 。

提醒 l 由於 Arty Z7-10 中的 FPGA 較小,該平台僅包含非常基本的影像處理功能。若有影像處理需求,請選購 Z7-20。

Zynq APSoC架構與配置

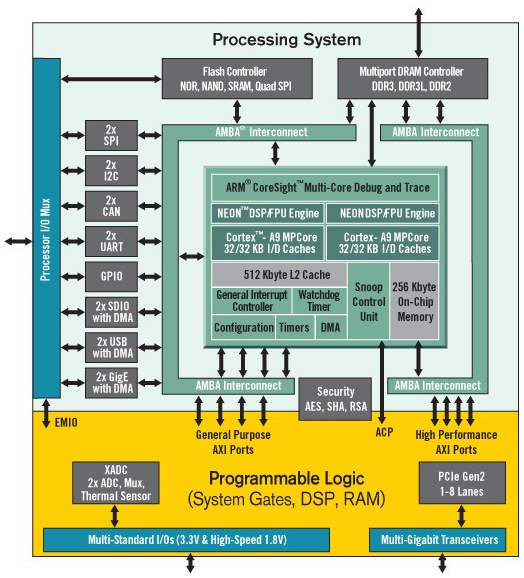

Zynq APSoC分為兩個不同的子系統:處理系統(PS)和可編程邏輯(PL)。

下圖顯示了 Zynq APSoC 架構的概述,PS 顏色為淺綠色,PL 為黃色。PL 幾乎與 Xilinx 7系列 Artix FPGA 完全相同,只是它另包含幾個專用介面,可緊密耦合到 PS。 PL 也不包含與典型 7 系列 FPGA 相同的硬體配置,必須由處理器或 JTAG 介面直接配置。 PS 由許多組件組成,包括應用處理單元(APU,包括2個Cortex-A9處理器)、高級微控制器總線架構(AMBA)互連、DDR3內建記憶體控制器和各種外接控制器,其 輸入/輸出 多路復用的專用 pin 腳達 54 個(Multiplexed I/O 或 MIO pin)。

注意 l Zynq-7020或Zynq-7010設備上不提供PCIe Gen2控制器與Multi-gigabit transceivers

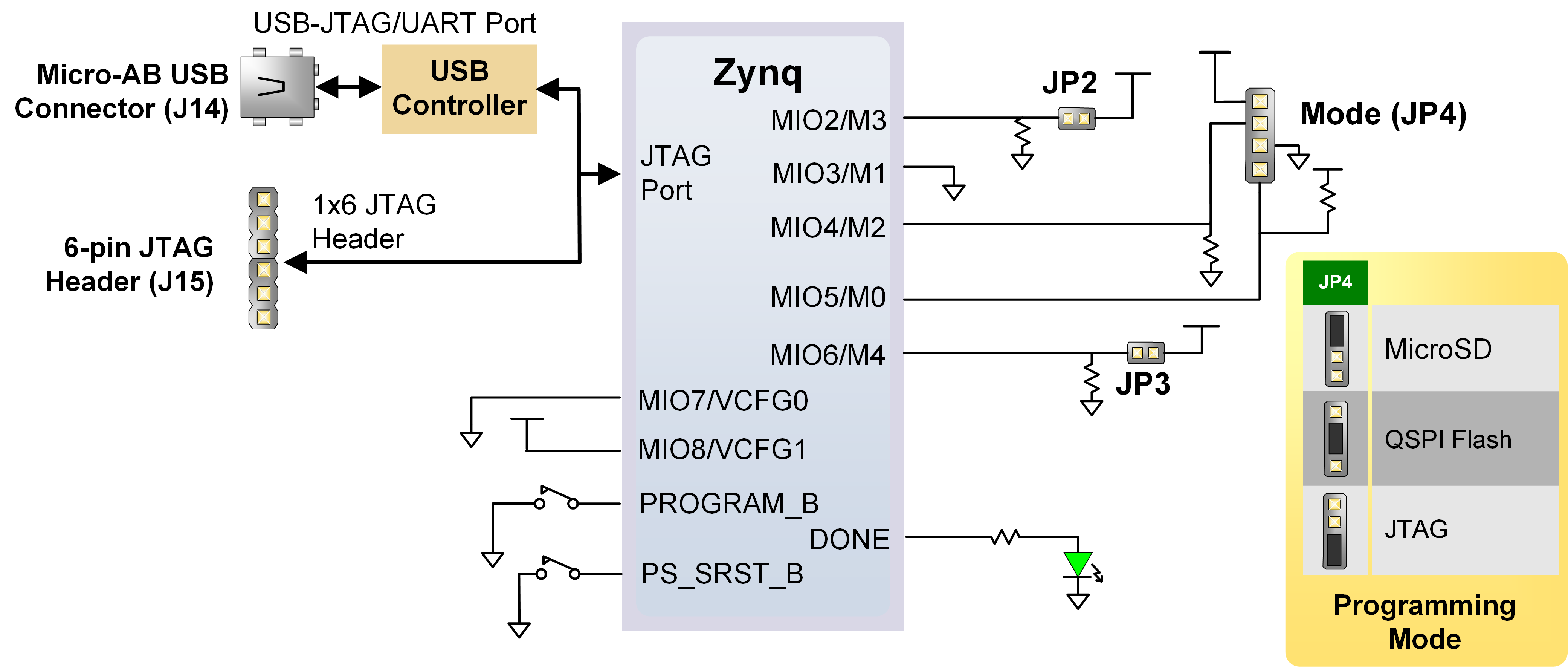

與 Xilinx FPGA 不同,Zynq-7020 的 APSoC 是圍繞處理器設計的,故 Zynq 引導過程與 FPGA 相比,更類似於微控制器。 啟動過程分為三個階段:第一級引導加載程序(FSBL)、配置可編程邏輯的比特流(可選)和使用者應用程序。 Arty Z7支持三種不同的啟動模式:microSD、Quad SPI Flash 與 JTAG。使用模式跳線(JP4)選擇啟動模式,該跳線會在上電後影響 Zynq pin腳配置的狀態。下圖說明了 Zynq pin腳如何連接在 Arty Z7 上。

規格版本

為滿足開發者對性能、資源和硬體成本的差異需求,Arty Z7 有兩個版本供開發者選擇:Arty Z7-10 與 Arty Z7-20。Z7-10 和 Z7-20 之間的區別是 Zynq 的功能與連接器上可用的 I/O 量。 Zynq 處理器具有相同的功能,但 Z7-20 的內部 FPGA 較大,約為 Z7-10 的 3 倍。在 Z7-10上,數位屏蔽(IO26-IO41)與 IOA(也稱為 IO42 )的內部未連接到 FPGA,A0-A5 只能用於模擬輸入。但這不會影響大多數現有 Arduino 的功能,因為大多數不使用此內部數位訊號。

| Arty Z7-10 | Arty Z7-20 | |

| FPGA part | XC7Z010-1CLG400C | XC7Z020-1CLG400C |

| 1 MSPS On-chip ADC | Yes | Yes |

| Processor | Dual ARM Cortex A9 | Dual ARM Cortex A9 |

| Look-up Tables (LUTs) | 17,600 | 53,200 |

| Flip-flops | 35,200 | 106,400 |

| Block RAM | 270 KB | 630 KB |

| Clock Management Tiles | 2 | 4 |

| Available Shield I/O | 26 | 49 |

軟體支援

Arty Z7 與 Xilinx Vivado 完全相容,可將 FPGA 邏輯設計與嵌入式 ARM 軟體開發融合,可用於設計任何複雜的系統。在設計中不須使用處理器者,也可以將 Zynq AP SoC 視為獨立的 FPGA。從 Vivado 2015.4 版本後,Vivado 可以免費用於所有WebPACK,而 Arty Z7 也包括其中。 Logic Analyzer 的 HLS 工具可將 C code 轉為 HDL code。

Arty Z7 也十分適用於Linux嵌入式設計。 Digilent 提供 Petalinux 功能,可以讓 Atry 的使用者快速啟動使用 Linux 系統。

Arty Z7 亦可用於 Xilinx SDSoC 環境,可在完全 C / C ++ 環境中輕鬆設計FPGA加速程序。

提醒 l Vivado 舊版 Xilinx ISE / EDK 工具集的使用者可以選擇在該工具集中使用 Arty Z7,但 Digilent 針對舊版本提供之使用資訊較少。

與PYNQ-Z1的區別

Arty Z7-20 與 PYNQ-Z1 共享完全相同的 SoC。 但 Arty Z7-20 沒有microphone input,但增加了一個 Power-on Reset 按鈕。

規格

ZYNQ處理器

- 650MHz 雙核心 Cortex-A9處理器

- 具有8個DMA通道的DDR3記憶體控制器與4個高性能AXI3介面

- 高頻寬週邊控制器:1G乙太網路 / USB 2.0 / SDIO

- 低頻寬週邊控制器:SPI / UART / CAN / I2C

- 可從JTAG / Quad-SPI / microSD卡 進行程式編輯

- 等效於Artix-7 FPGA的可程式設計邏輯

儲存

- 支援16位元匯流排, 1050 Mbps的 512MB DDR3

- 16MB 四路 SPI 快閃記憶體,全球唯一的EUI-48/64™48位元相容識別標示

- 支援microSD擴充

功率

- 由USB或任何7V-15V外部電源供電

USB和乙太網路

- 千兆乙太網路 PHY

- USB-JTAG程式設計介面

- USB-UART通訊介面

- USB OTG PHY介面(僅支援主機)

音訊和視訊

- HDMI高畫質輸入/輸出

- 附3.5mm插孔的PWM驅動單聲道音訊輸出

開關、按鈕和LED

- 4 個按鈕

- 2 個滑動開關

- 4 個LED

- 2 個RGB LED

擴充介面

- 2 個標準Pmod連接埠,總計 16 個 FPGA I/O

- Arduino / chipKIT Shield 介面

- 總計多達 49 個 FPGA I/O

- 6 個單向 0-3.3V 模擬輸入到 XADC

- 4 個插分 0~1V 類比輸入到 XADC

更多產品訊息

| 產品文件:產品規格表 / 電路圖 / 中文型錄 | |

|

產品編號: |

|

| 410-346-10 (Arty Z7-10) | |

|

410-346-20 (Arty Z7-20) 471-053(Arty Z7-10 with USB A to Micro-B Cable) 471-054(Arty Z7-20 with USB A to Micro-B Cable) |

|

|

471-006 (Arty Z7-20 含 Zynq SDSoC Voucher,不含Vivado Design Suite) 影音應用建議購買此版本 |

|

|

iopenmall:Arty Z7 : Xilinx APSoC Zynq-7000 開發板 蝦皮賣場:Arty Z7 : Xilinx APSoC Zynq-7000 開發板 |