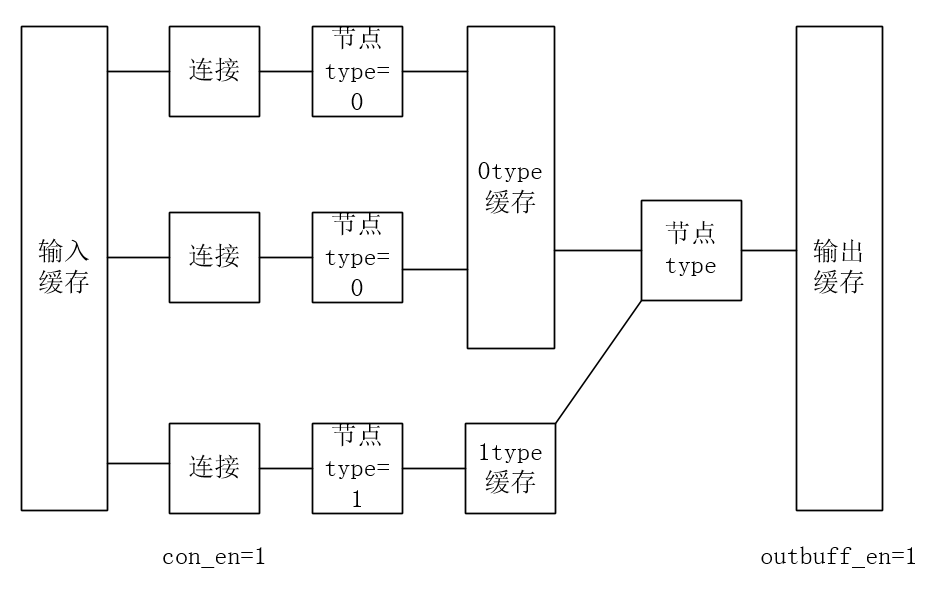

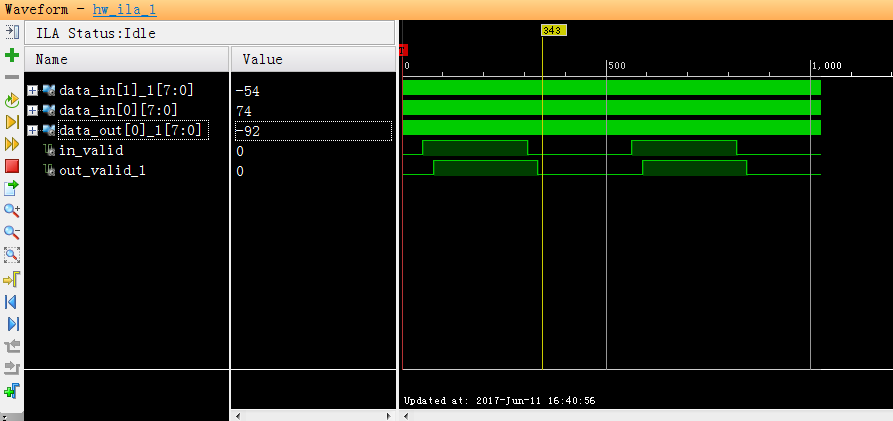

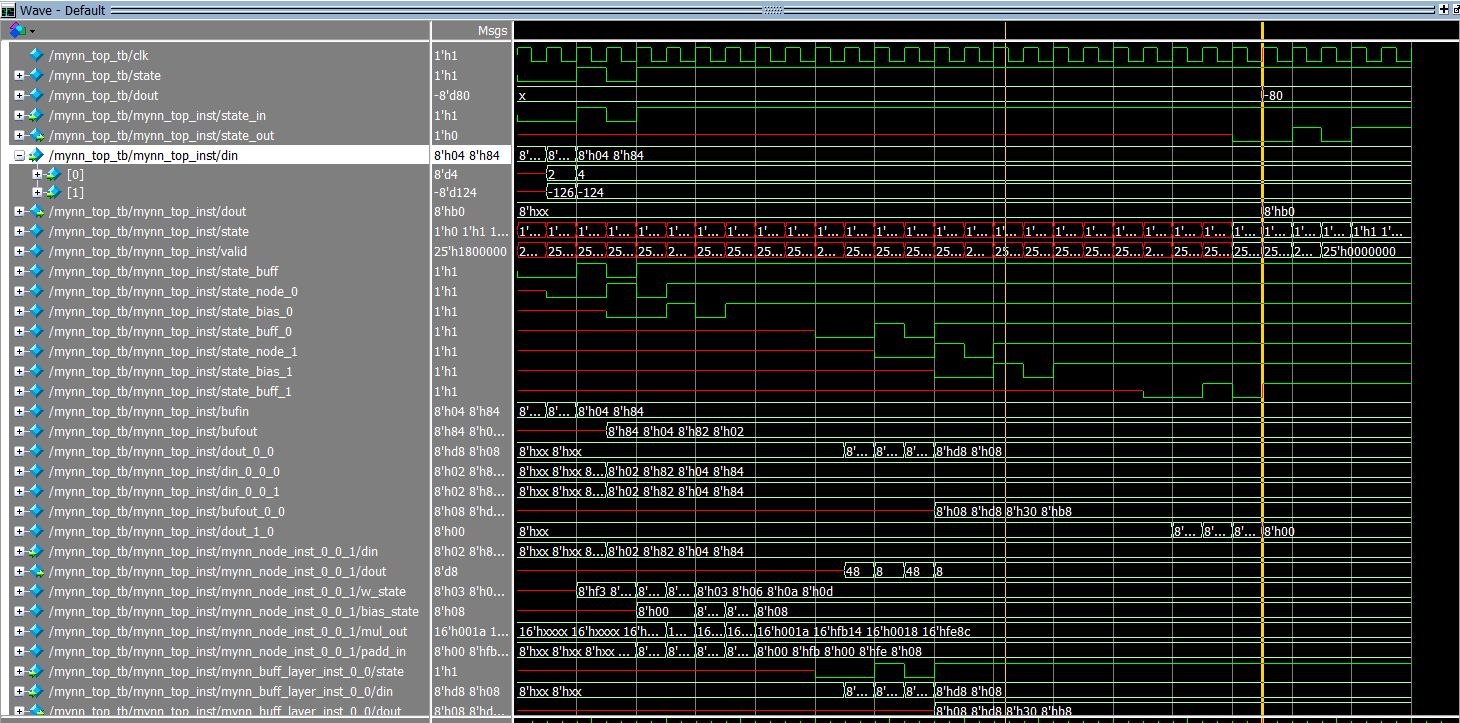

本文主要講述一個內建 Python 介面的 FPGA 神經網路推斷過程加速器 IP ,透過這個工具用 Python 快速產生一套針對特定稀疏連接優化的神經網絡加速器 HDL 設計。產生的語言為 Systemverilog hdl。v1.0中實現功能包括:任意連接方式(前向/前向跨層)、並行程度可設(整數倍矩陣乘法行分片)、tanh 啟動函數。

相較於軟體設計,硬體設計要考慮問題會更多。本文做 IP 設計以簡化不同參數的神經網路加速器設計過程。透過 Python 語言產生 HDL,便於Python 研究者在 FPGA 算法加速方面的設計。可達到以下的創新特色:

1. 基於 Python語言,對日常用 Python 做演算法模擬的研究者提供更為友好的方式

2. 靈活的可配置性

3. 針對特定的參數自動進行結構優化

(本文為2017 DDC中國區選拔賽參賽作品)

神經網絡FPGA加速器IP

http://www.digilent.com.cn/project/details/135.html