# uno A10 GX1150 Prototyping System

10010100010111000101000010001110011

### **Product Summary**

The proFPGA uno A10 GX1150 system is a complete and modular FPGA solution, which meets highest requirements in the area of FPGA based Prototyping. It addresses customers who need a scalable and flexible high speed ASIC Prototyping and IP verification solution for early software development and real time system verification. The innovative system concept offers highest flexibility and reusability reconfigurability for several projects, which guarantees the best return on investment.

### **Highest Flexibility**

The system architecture is based on a modular system concept. The FPGAs are assembled on dedicated single-chip FPGA modules, which will be plugged on the proFPGA uno, duo or quad motherboard. This offers the highest flexibility to use for example different FPGA types on the same motherboard. The user has access to almost all I/Os of the FPGA, which gives him maximum freedom regarding the FPGA interconnection structure. This way the prototyping system can be adapted in the best way to any user design. Furthermore the system offers a total of 6 extension sites on the top and bottom site for standard or user specific extension boards like DDR4 memory, PCle gen1/2/3, Gigabit Ethernet, USB 3.0 or other high speed interfaces.

### Maximum Performance

The well designed boards of the proFPGA system are optimized and trimmed to guarantee best signal integrity and to achieve highest performance. The high speed boards together with specific high speed connectors allow a maximum point-to-point speed of up to 1.0 Gbps single ended over the standard FPGA I/Os and up to 17.4 Gbps differential over the high speed serial transceivers of the FPGA. This performance allows the designer to run his design at the highest possible speed on the proFPGA system.

### **Biggest Capacity**

Equipped with one Intel<sup>®</sup> Arria<sup>®</sup> 10 FPGA module, the proFPGA uno system can handle up to 8 M ASIC gates on only one board.

### Very User Friendly

The proFPGA prototyping system provides an extensive set of features and tools, like remote system configuration, integrated self and performance test, automatic board detection, automatic I/O voltage programming, system scan and safety mechanism, which simplifies the usage of the FPGA based system tremendously. 000011101001101000101

101010000101110000011101001101000101 1010000101110000011101001101000101

### Key Features

- 8 M ASIC gates capacity on one board

- 646 user I/Os

- 48 dedicated high speed serial transceivers

- 6 individually adjustable voltage regions

- Up to 1.0 Gbps single ended point-to-point speed

- Up to 17.4 Gbps with high speed transceivers

- Smart Stacking Technology (SST)

- High performance host interface (DMBI)

- proFPGA Builder Software

### Innovative Technologies

### Smart Stacking Technology

- Board detection when boards are plugged

- Automatic and right I/O voltage setting and programming with conflict detection

- Integrated interconnection self and performance test

- Smart I/O resource management. No I/O resources get lost or blocked by connectors

### FPGA Mixing Technology

- Easy plugging and unplugging of FPGA modules on motherboards

- Various FPGAs from different vendors can be mixed

- Automatic scan and detection of FPGA modules, when plugged

- Different FPGA configurations are controlled by proFPGA Builder software

#### Device Message Box Interface

- High speed, low latency data exchange system

- Enables various use modes and functionalities like remote system configuration and monitoring, debug, application level programming and co-simulation

- Up to 3.5 Gbps data transfer rateRuns over USB, Ethernet or PCIe

### Advanced Clock Management

- \*\* 8 fixed clocks

- Run-time configurable local clocks

- Each clock with sync signals

## uno A10 GX1150 Prototyping System

| profpga uno A10 GX1150 Specification |                                                                                                                                                                                                               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA                                 | - 1 x Intel Arria 10 GX1150 F1932 FPGA                                                                                                                                                                        |

| Capacity                             | - 8 M ASIC gates on one board                                                                                                                                                                                 |

| FPGA-internal memory                 | - 54,26 Mbit                                                                                                                                                                                                  |

| Signaling rate                       | - Up to 1.0 Gbps single ended (standard I/O)/ up to 17.4 Gbps differential                                                                                                                                    |

| Extension sites                      | - 6 Extension sites with high speed connectors                                                                                                                                                                |

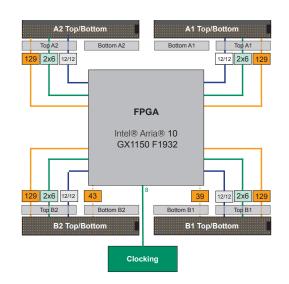

| I/O resources                        | <ul> <li>Overall 646 signals for I/O and inter FPGA connection</li> <li>4 x 141 I/Os to top side connectors</li> <li>1 x 43 and 1 x 39 I/Os top side connectors</li> </ul>                                    |

| High speed I/O transceivers          | <ul> <li>- 48 dedicated transceivers running up to 17.4 Gbps</li> <li>- 4 x 12 transceivers to top side connectors</li> </ul>                                                                                 |

| Available interface boards           | - USB 3.0, PCIe Gen2/Gen3, MIPI, DVI, DDR3 memory, Gb Ethernet, etc.                                                                                                                                          |

| Voltage regions                      | <ul> <li>- 6 individually adjustable I/O voltage regions</li> <li>- Stepless from 1.2V up 1.8V on 6 extension sites</li> <li>- Automated detection of daughter cards and setting of right voltages</li> </ul> |

| Clocking                             | - 8 fixed global clock and sync inputs<br>- use of up to 2 x 6 clock-capable I/Os per connector                                                                                                               |

| Configuration                        | - From host via Ethernet, USB or standalone over USB stick or Xilinx JTAG                                                                                                                                     |

| Data exchange                        | <ul> <li>On board DMBI (Device Message Box Interface)</li> <li>Data exchange rate:</li> <li>Ethernet (up to 100 Mbps), USB (480 Mbps)</li> </ul>                                                              |

| Power                                | External (optional) ATX Power Supply (12 V, 24 - 35 A output)                                                                                                                                                 |

| Dimensions                           | - 5.91" x 0.95" x 5.91" / 150 mm x 24 mm x 150 mm (width x height x depth)<br>- 0.5 kg weight                                                                                                                 |

#### profpga uno A10 6X1150 I/O and Clock Architecture